# PCIEC-85 PCI Express® Jumper

# High Speed Designs in PCI Express® Applications Generation 3 - 8.0 GT/s

**Copyrights and Trademarks** Copyright © 2015 Samtec, Inc.

### **Application Note**

# <u>samtec</u>

Series: PCIEC-85, PCI Express® Jumper Cable Assembly, 85 ohm Standard: PCI Express, Generation 3, 8 GT/s

#### COPYRIGHTS, TRADEMARKS, and PATENTS

Final Inch<sup>™</sup> is a trademark of Samtec, Inc. Other product names used herein are trademarks of their respective owners. All information and material in this publication are property of Samtec, Inc. All related rights are reserved. Samtec, Inc. does not authorize customers to make copies of the content for any use.

#### Terms of Use

Use of this publication is limited to viewing the pages for evaluation or purchase. No permission is granted to the user to copy, print, distribute, transmit, display in public, or modify the contents of this document in any way.

#### Disclaimer

The information in this publication may change without notice. All materials published here are "As Is" and without implied or expressed warranties. Samtec, Inc. does not warrant this publication will be without error, or that defects will be corrected. Samtec, Inc. makes every effort to present our customers an excellent and useful publication, but we do not warrant or represent the use of the materials here in terms of their accuracy, reliability or otherwise. Therefore, you agree that all access and use of this publication's content is at your own risk.

NEITHER SAMTEC, INC. NOR ANY PARTY INVOLVED IN CREATING, PRODUCING, OR DELIVERING THIS PUBLICATION SHALL BE LIABLE FOR ANY DIRECT, INCIDENTAL, CONSEQUENTIAL, INDIRECT, OR PUNITIVE DAMAGES ARISING OUT OF YOUR ACCESS, USE OR INABILITY TO ACCESS OR USE THIS PUBLICATION, OR ANY ERRORS OR OMISSIONS IN ITS CONTENT.

# Abstract

The PCI Express® is primarily intended as a high performance serial interface targeted for use in desktop, mobile, workstation, server, communications platforms, and embedded devices. As with any modern high speed serial design, the performance of an actual PCI Express® interconnect is highly dependent on the implementation. Recent advances in technology have allowed PCI Express® designs to reliably reach 8.0 GT/s using common PCB materials and advanced Tx and Rx equalization techniques. This paper describes a statistical simulation compliance method applied to proven Samtec designs. This application note is intended to help engineers deploy systems of two PCB cards connected through Samtec's family of high speed PCI Express® Jumper 85 ohm cable assemblies.

To demonstrate the feasibility of using Samtec's PCIEC PCI Express® 85 ohm Jumper cable assembly mated with a PCIE high speed socket with standard FR4 epoxy PCBs, statistical simulations will be used to characterize the full Tx die-to-Rx die PCIE 8.0 GT/s channel, utilizing Samtec Final Inch<sup>™</sup> s-parameter modeling of the connector and complete interconnect channel, including all aggressor crosstalk impacts.

# Introduction

Samtec has developed a full line of connector products that are designed to support serial speeds up to 8 GT/s, the maximum transfer rate of each PCI Express® data lane. Working with Teraspeed Consulting, they have developed a complete breakout and routing solution for each member of the Samtec line of high speed connectors, called Final Inch<sup>™</sup>.

To demonstrate the feasibility of using Samtec PCIEC 85 ohm Jumpers and connectors in PCI Express® applications with standard FR4 epoxy PCBs, s-parameter models of the mated connectors and PCBs, along with statistical simulation techniques, will be used to sweep various cable lengths across the design space to show a final compliance region.

# The PCI Express® Specification

PCI Express® 8.0 GT/s links are based on recent advances in signal processing technology using advanced Tx and Rx equalization. A PCI Express® link is comprised of a dual-simplex communications channel between two components physically consisting of two low-voltage, differential signal pairs. The PCI Express® Base Specification defines one half of a link (one transmitter and receiver) as an electrical sub-block. The design model used for this paper is of three electrical sub-blocks operating in tandem, one the victim surrounded by 2 aggressors, with all bit streams heading in the same direction.

Detailed specifications for an electrical sub-block can be found starting in Section 4.3 of the PCI Express® Base Specification and will be referred to throughout the rest of this paper. Detailed channel specifications start in Sub-section 4.3.6. Channel compliance testing requirements of subsection 4.3.6.4 for 8.0 GT/s were adhered to for these simulations. See PCI Express® Base Specification Revision 3.0 for more details.

## The Simulation Model

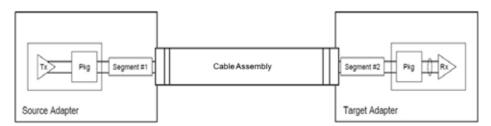

Figure 1 shows the mated Samtec PCIEC series cable assembly used in a typical multi-segment channel with a source adapter residing on a motherboard and a target adapter residing on an add-in card. The test circuit is modeled as:

- Agilent's Advanced Design System Tx and Rx modules that correlate to the Tx and Rx package models released by the PCI Special Interest Group, and defined in Section 4.3.6 Channel Specification of the PCI Express® Base Specification, Rev 3.0.

- A fixed length interconnect trace segment on the source adapter, with and without a 200 nF capacitor

- A fixed length interconnect trace segment on the target adapter.

- Two mated Samtec PCIE-RA series right-angle connector touchstone sparameter models.

- A variable length RLGC model of Samtec TX-3285 twinax cable

Figure 1 - PCI Express® 8 .0 GT/s Test Configuration

The RLGC cable model was swept using multiple lengths of Source and Target traces to determine the limits of compliant channel operation.

- 1. Source length =  $10^{\circ}$  and Target length =  $4^{\circ}$ .

- 2. Source length equal to target length set at 4", which is the typical maximum length for PCIE add-in cards.

- 3. Source length = 1" and Target adapter = 1", with 200nF DC blocking capacitor.

For sweep configurations #1 and 2 additional simulations were performed with the addition of 200 nF DC blocking capacitors, to model additional signal quality degradation.

<u>samtec</u>

**Series:** PCIEC-85, PCI Express® Jumper Cable Assembly, 85 ohm **Standard:** PCI Express, Generation 3, 8 GT/s

All traces were modeled as microstrip on FR4 with the following parameters:

- FR4 is modeled using a Svensson/Djordjevic causal model that has a broadband response that is faithful to measured results from DC to greater than 20 GHz, using the following parameters:

- Er = 4.2 @ 1 GHz

- Loss Tangent = 0.02 @ 1 GHz

- Copper is modeled as follows to reflect the reduced conductivity of copper foil used in PCB fabrication:

- Conductivity = 4.5E+7 S-m

- Surface roughness = 0.6 micron

- Traces are differential microstrip with the following geometry:

- o 85 ohm differential impedance

- o 7 mil trace width

- 2 mil trace copper thickness

- o 5 mil center-to-center spacing

- o 4.4 mil FR4 dielectric thickness

- No differential coupling to neighboring differential channels

Using other trace geometries or materials will lead to different results than shown here. However, if reasonable care is made to stay well within the design space and guidelines provided in this document, it is possible to build robust PCIE 8.0 GT/s channels with limited additional simulation verification.

<u>samtec</u>

**Series:** PCIEC-85, PCI Express® Jumper Cable Assembly, 85 ohm **Standard:** PCI Express, Generation 3, 8 GT/s

## The Simulation Environment

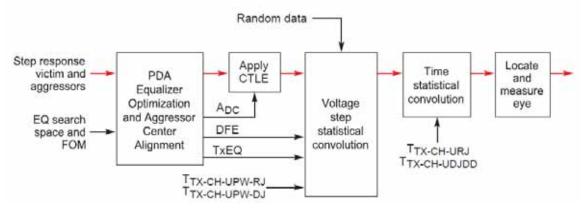

The PCI Express® Base specification requires that 8.0 GT/s channel compliance be performed utilizing a die-to-die interconnect model, including the Tx and Rx packages. "The model shall include both victim and a sufficient number of aggressor paths to accurately capture the channel crosstalk effects. Using the Tx voltage and jitter limits defined in the transmitter specification ... it is possible to transform these parameters to what would appear at the die pad of a Tx" [sic]. As shown in Figure 2, the output of the simulation is actually the eye as it appears at the input of the Rx sample latch.

Figure 2 - PCI Express® 8.0 GT/s Flow Diagram for Channel Tolerance

The PCI Special Interest Group (SIG) provides an open source statistical eye simulator (SEASIM v0.46) that may be used to implement the following necessary simulation and modeling requirements:

- Channel characteristics defined as s-parameters.

- Behavioral Tx and Rx package models.

- Transmitter jitter and voltage.

- Transmitter and receiver termination impedance of 2 x 42.5 ohm.

- Time domain representation of the end-to-end connectivity.

- Behavioral Tx equalization.

- Behavioral Rx continuous time linear equalizer (CTLE).

- Behavioral Rx digital feedback equalizer (DFE).

- Optimization of Tx equalization and Rx DFE/CTLE settings.

- Statistical treatment of jitter.

- Statistically defined output eye width and eye height.

# <u>samtec</u>

**Series:** PCIEC-85, PCI Express® Jumper Cable Assembly, 85 ohm **Standard:** PCI Express, Generation 3, 8 GT/s

For this application note, Agilent's Advanced Designed System 2011.10 (ADS2011) software simulation tool is used to accomplish the simulation tasks. Templates were developed within ADS to automate the analysis so that channel components can be easily replaced. The results from SEASIM and ADS are the same provided the same source jitter and equalization settings are used. The ADS templates require the following channel definitions:

- Definition of input S-parameter files to be used in the simulations.

- Samtec PCIEC mated connectors, a fixed length of Source and Adapter Cards.

- PCIE3 Tx and Rx package models

- Definition of RLGC cable lengths to be simulated.

- Iterative processing of all cable lengths and preset settings using the ADS2011 batch simulation mode.

- FR4 Microstrip Differential Trace

- 200 nF capacitor

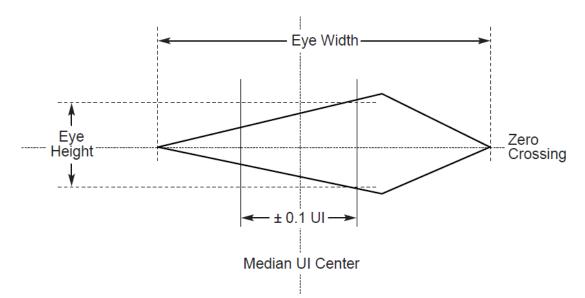

#### Compliance Eye Mask

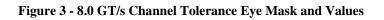

Figure 3 shows the 8.0 GT/s channel compliance eye mask. The ADS2011 channel simulator and Samtec modeling provide all necessary inputs required to generate the statistical eye necessary to test against the eye mask pass/fail requirements. Although the specification allows for a minimum measured eye height of 25 mV P-P, we will de-rate the specification to 50 mV P-P for the purposes of this study, to provide a guard band for "the things that keep engineers awake at night." Or at least the things that keep this author awake. This guard band should be sufficient to provide designers using this document additional confidence.

| Table 4-27: | Channel Tolerancing Eye Mask Values |  |

|-------------|-------------------------------------|--|

|-------------|-------------------------------------|--|

| Symbol                                                                | Parameter                     | Value     | Units | Comments                                      |

|-----------------------------------------------------------------------|-------------------------------|-----------|-------|-----------------------------------------------|

| V <sub>RX-CH-EH</sub>                                                 | Eye height                    | 25 (min)  | mVPP  | Eye height at BER=10 <sup>-12</sup> . Note 1. |

| T <sub>RX-CH-EW</sub>                                                 | Eye width at zero<br>crossing | 0.3 (min) | UI    | Eye width at BER=10 <sup>-12</sup>            |

| T <sub>RX-DS-OFFSET</sub> Peak EH offset from<br>UI center            |                               | ±0.1      | UI    | See Figure 4-87 for details.                  |

| V <sub>RX-DFE_COEFF</sub> Range for DFE d <sub>1</sub><br>coefficient |                               | ±30       | mV    | See Figure 4-70 for details.                  |

#### Compliance Measurements

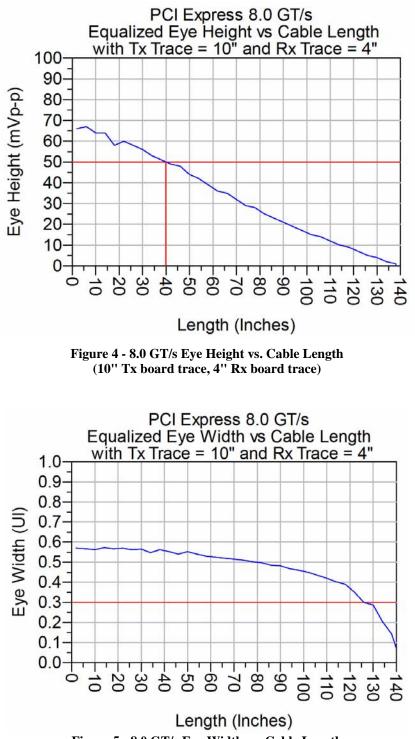

To obtain a feel for the overall range of operation of PCI Express® 8.0 GT/s channels simulation models were created with 10 inch Tx trace length and 4 inch Rx trace segments, the maximum length for a standard PCI Express® 8.0 GT/s add-in card, without DC blocking capacitors, where the cable RLGC model is swept from 4" to 144", for a total channel length from 18" to 158". Figure 4 displays a graph of the measured inner eye height for each simulated length. This simulation includes all channel, jitter, and crosstalk effects. Our chosen compliance limit of 50 mV P-P is shown on the chart as a red line. With the trace models and material parameters that we are using, a cable length of 40" or a total channel reach of 54" is possible. Longer channels will have higher loss, with lower eye openings; however, we generally do not advise using longer channels without detailed channel modeling.

Figure 5 displays a graph of the measured inner eye width for the same simulation deck as Figure 4. The 0.3 UI eye width compliance limit is shown as a red line on the chart. Clearly there is sufficient jitter margin at any of our simulated channel lengths. This is typical for well-behaved, resonance free interconnect systems, which are generally not jitter limited, and are limited by the received signal amplitude.

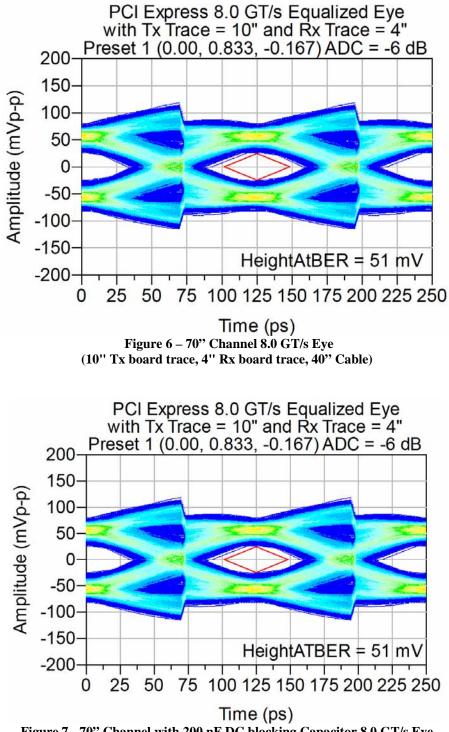

The simulated eye for the 54" channel, 40" of cable interconnect (10" Tx board trace and 4" Rx board trace) is shown in Figure 6. For these statistical simulations the eye boundary is defined for a statistical confidence interval with a bit error rate (BER) of 10<sup>-12</sup>, as required by the PCI Express® specification. An inner eye opening of 51mV was measured by the simulator; this is just at our established compliance limit for this study. The measured inner eye width of 0.50 UI is well above our 0.3 UI limit.

By providing 25 mV of additional amplitude margin over the specified 25 mV limit, we provide a guard against additional issues that may be unforeseen by the designer. The impact of adding 200 nF DC blocking capacitors to this same model is shown in Figure 7. For these long reach PCI Express® channels, the impact of a well-designed blocking capacitor pad pattern is essentially negligible, due to the dominance of dielectric and conductor losses.

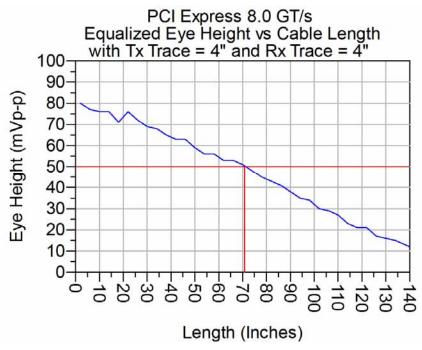

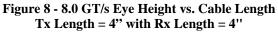

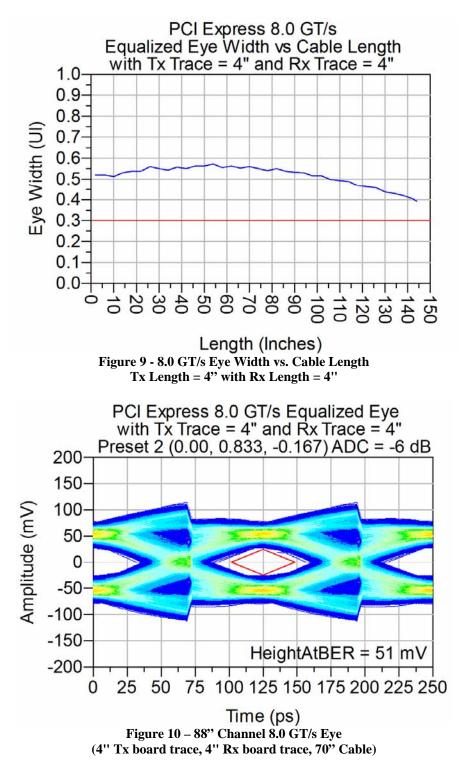

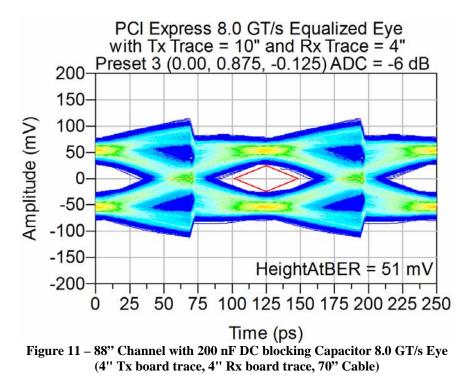

If we set the length of the Tx source card to 4" and keep the Rx adapter to 4", we can now sweep the cable length from 4" to 144" and view the results. Figure 8 shows a plot of the measured eye height vs. cable length, resulting in a channel length of 78" (cable length of 70"). Figures 9 and10 show the representative eyes for the 78" channels, with and without DC blocking capacitors. As seen previously, addition of the capacitor has a negligible impact on these long reach channels.

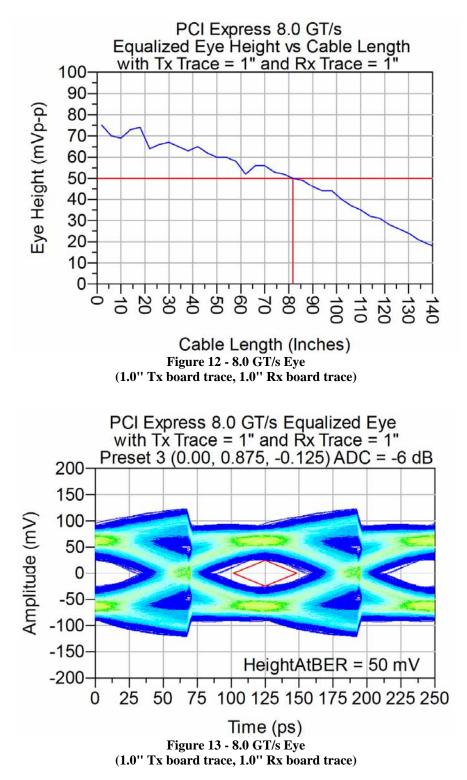

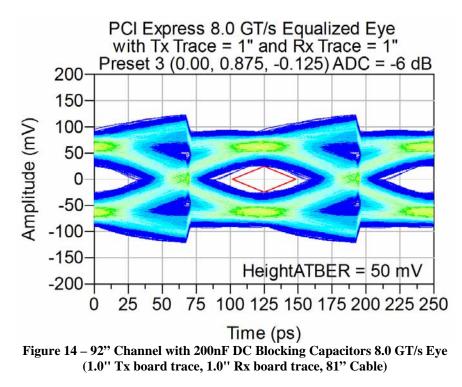

A simulation sweep of extremely short Tx and Rx trace segments of 1" is used to characterize the PCIEC Jumper cable assembly by itself. Figure 12 shows a graph of the inner eye height of each simulated cable length for maximum cable length of 83" (total channel length of 81"). Figure 14 shows the eye diagram of the 83" channel. Reducing the loss effect associated with the Tx and Rx traces the overall cable reach can be greatly increased.

### Conclusions

A mated PCIEC Series Cable Assembly in a board-to-board configuration can be used in 85 ohm PCI Express® 8.0 GT/s systems with total channel lengths can reach up to a 54 total inches - depending on the Tx and Rx trace lengths - and when used with Samtec's Final Inch<sup>™</sup> routing, breakout, and trace width solutions as modeled and simulated in this document.

Because loss is the dominant contributor to system degradation, designers should be aware that using smaller trace widths, laminates with higher loss tangent, sub optimal routing solutions with higher pair-to-pair coupling, and additional vias will decrease overall performance and the maximum allowable trace length.

It is advisable, when designing systems that approach the maximum trace length limits, to perform detailed modeling, simulation, and measurement of the target design including the effects of material properties, traces, vias, and additional components.