## Designing DC-Blocking Capacitor Transitions to Enable 56Gbps NRZ & 112Gbps PAM4

Scotty Neally, Samtec Teraspeed Consulting Scott McMorrow, Samtec Teraspeed Consulting

## **Speakers**

#### **Scotty Neally**

Signal Integrity Consultant

Samtec Teraspeed Consulting

Scotty Neally is an experienced signal integrity consultant with a background in high density PCB design and measurement, automation of signal integrity design flows, and currently focuses on system design for emerging technologies.

#### **Scott McMorrow**

CTO, Signal Integrity Products

Samtec Teraspeed Consulting

Scott McMorrow is an expert in high-performance design and signal integrity engineering, with a broad background in complex system design, interconnect and signal integrity engineering, modeling and measurement methodology, and professional training, spanning over 25 years.

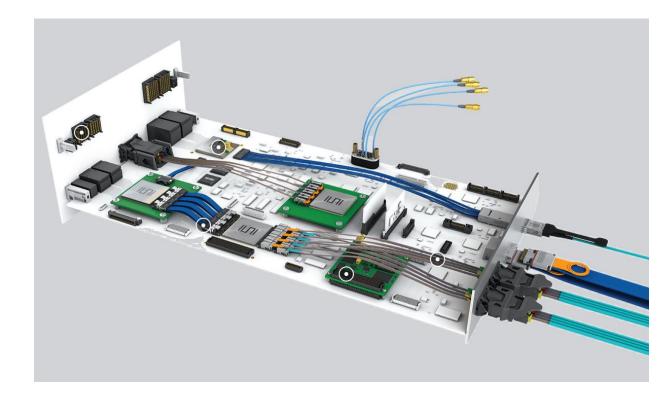

## **System Design**

- Tradeoffs

- Cost

- Leadtime

- o Performance

- Reliability

**Decision Diagram**

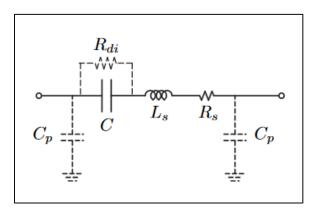

## **Traditional Capacitor Models**

**Shorting Resistor**

**PEC Plane**

**RLC Model**

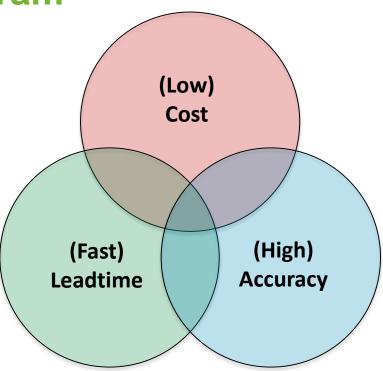

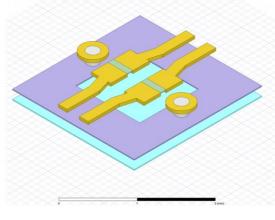

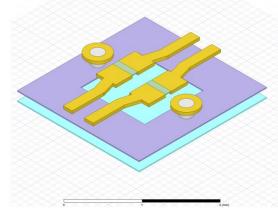

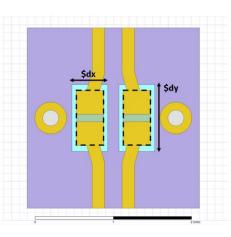

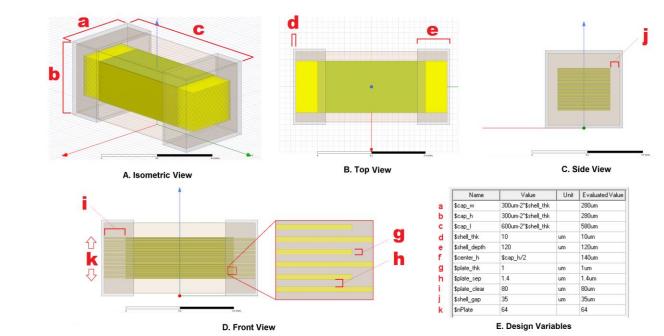

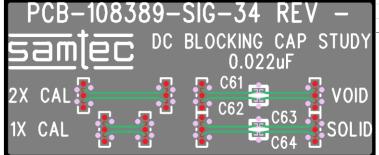

## **DC Blocking Capacitor Design Layout**

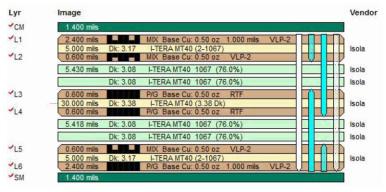

## **Design Optimization**

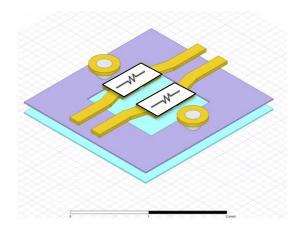

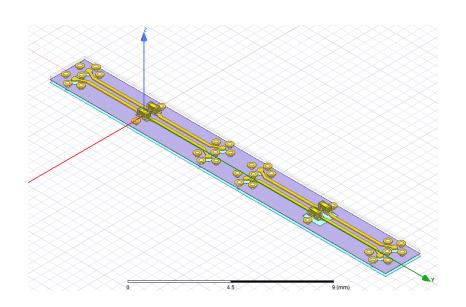

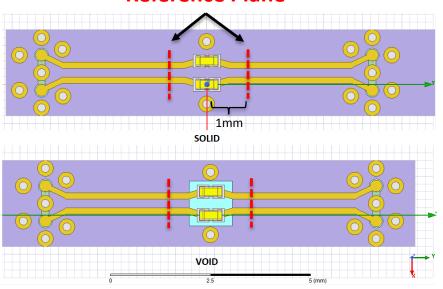

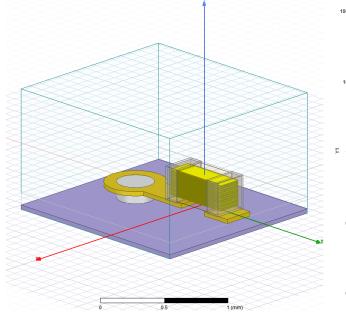

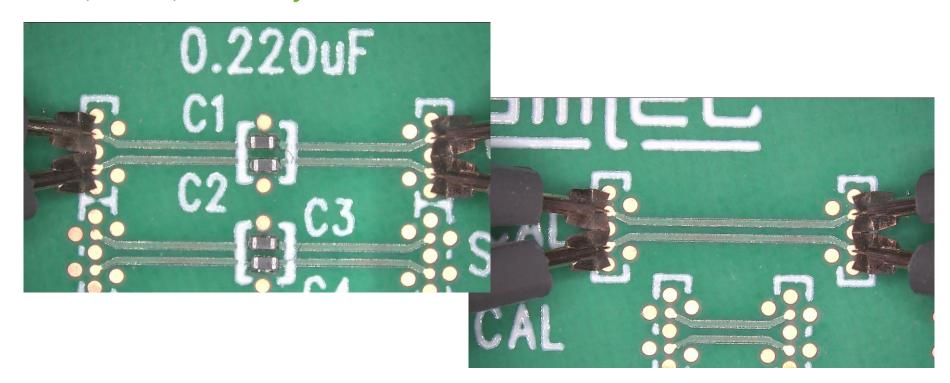

## **Test Vehicle Preview**

#### De-embedded Reference Plane

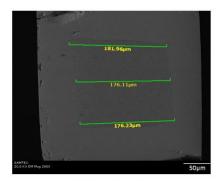

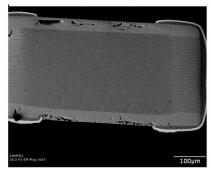

## **MLCC SEM Measurements**

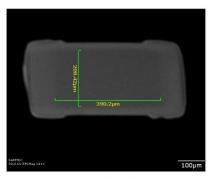

A. Side View

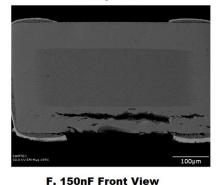

E. 220nF Front View

**B.** Top View

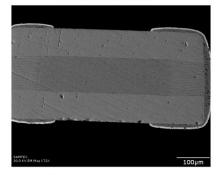

C. Cross-Section

G. 47nF Front View

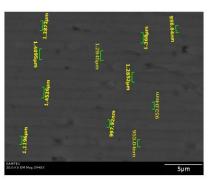

D. Line Scan

H. 22nF Front View

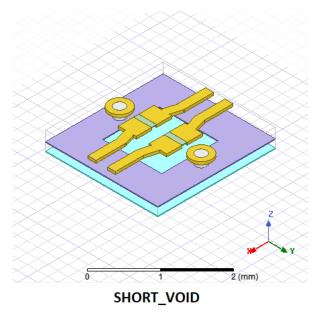

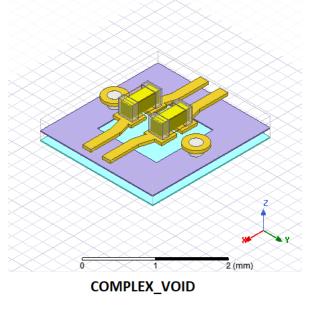

## **HFSS Model**

$$C = \frac{E_o * E_r * n * A}{d}$$

C = capacitance

$E_o$  = vacuum permittivity

$E_{\rm r}$  = relative dielectric constant

n = number of layers (n + 1 electrodes)

A = area of electrode overlap

d = dielectric thickness between layers

| Case Size Capacitor Value (nF) |     | MFG, P/N                 | n Plates | Er   | Estimated<br>Capacitance (nF) | Tolerance (%) |

|--------------------------------|-----|--------------------------|----------|------|-------------------------------|---------------|

| 201                            | 220 | TDK, C0603X7S0J224K030BC | 90       | 5000 | 214.48                        | -2.51%        |

| 201                            | 150 | TDK, C0603X7S0J154K030BC | 64       | 5000 | 151.82                        | 1.21%         |

| 201                            | 47  | TDK, C0603X7S0J473M030BB | 40       | 2500 | 46.99                         | -0.02%        |

| 201                            | 22  | TDK, C0603X7S0J223K030BB | 20       | 2500 | 22.89                         | 4.06%         |

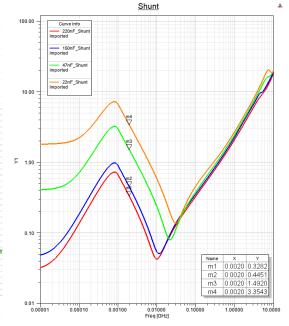

## **Shunt Simulation**

$$C = \frac{1}{2\pi * f * X_c}$$

|   | Simulated       | Simulated          | Capacitance   | Difference from |  |

|---|-----------------|--------------------|---------------|-----------------|--|

| ١ | Reactance X (Ω) | Capacitance C (nF) | Target C (nF) | Nominal (%)     |  |

| Ì | 0.3282          | 242.47             | 220           | 9.3%            |  |

|   | 0.4451          | 178.79             | 150           | 16.1%           |  |

|   | 1.4920          | 53.34              | 47            | 11.9%           |  |

|   | 3.3543          | 23.72              | 22            | 7.3%            |  |

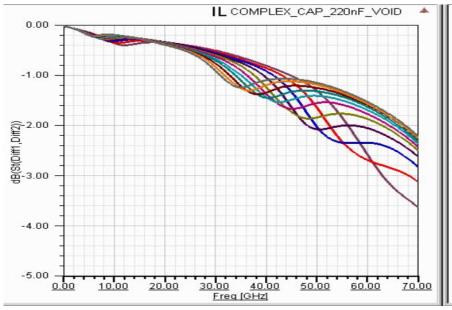

## 0201 PKG Family

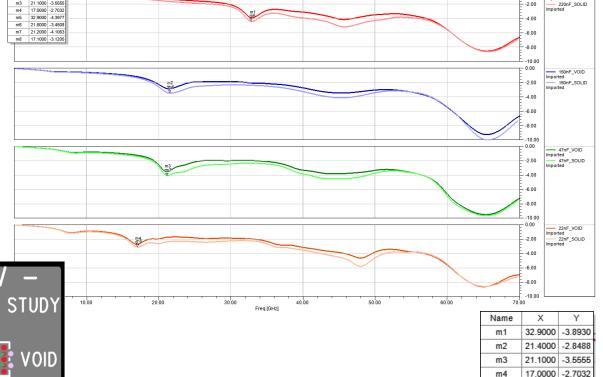

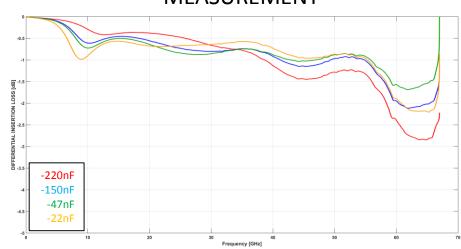

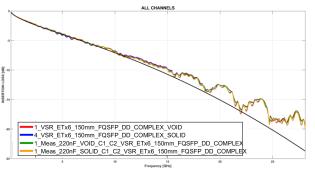

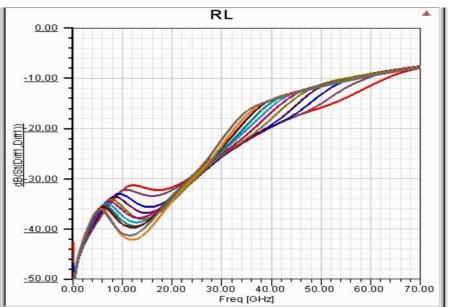

Using the test vehicle with 4 different capacitor values and 2 structures (VOID & SOLID) we compare the insertion loss of each

o 220nF, 150nF, 47nF, 22nF

Terminal S Parameter Plot 3 1

17.1000 -3.1205

32.9000

21.6000

21.2000

m5 m6

m7

-4.3977

-3.4508

-4.1063

fixture\_complexCAP\_220nF

220nF VOID

## **Capacitor Modeling**

**Sim to Measurement Comparison**

|        | Simulated<br>Measured<br>Both |                 |                  |                 |                |   |

|--------|-------------------------------|-----------------|------------------|-----------------|----------------|---|

|        | Value                         | Complex<br>VOID | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |   |

| 5      | 220nF                         | X               | Х                | Х               | Х              | 1 |

| $\neg$ | 150nF                         | Χ               | Χ                |                 |                |   |

|        | 47nF                          | Χ               | X                |                 |                |   |

|        | 22nF                          | X               | X                |                 |                |   |

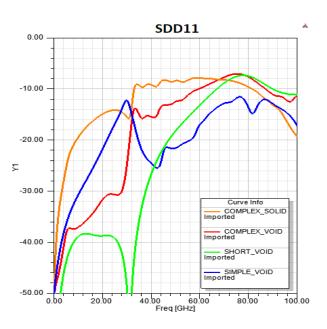

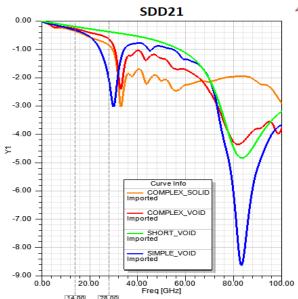

#### **Compare Capacitor Models**

- 1. SIM 220nF All Model Types

- 2. SIM 220nF/MEAS All Values Complex Model (VOID)

- 3. SIM 220nF/MEAS All Values Complex Model (SOLID)

#### **Channel Exploration**

- 4. SIM & MEAS 220nF, Chip to Module Host TX Pkg Only (high loss pkg)

- 5. SIM & MEAS 220nF, Chip to Module Optimistic TX/RX (low loss pkg)

## **What To Pay Attention To**

- How do simulation results vary between modeling structures?

- How do capacitor values for a given case size (0201) affect inductance?

- How does the transition geometry (SOLID vs VOID) impact channel performance?

- What impact does loop inductance have on these geometries?

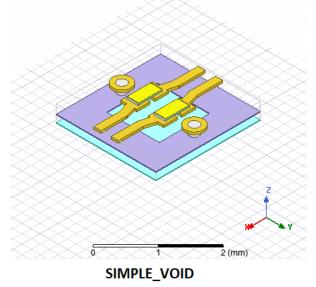

## 1. SIM - 220nF Capacitor, All Model Types

## 1. SIM - 220nF Capacitor, All Model Types

| Simulated<br>Measured<br>Both | Capacitor Models |                  |                 |                |   |  |  |

|-------------------------------|------------------|------------------|-----------------|----------------|---|--|--|

| Value                         | Complex<br>VOID  | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |   |  |  |

| 220nF                         | Х                | Х                | Х               | Х              | 1 |  |  |

| 150nF                         | Χ                | Χ                |                 |                |   |  |  |

| 47nF                          | Χ                | Χ                |                 |                |   |  |  |

| 22nF                          | X                | X                |                 |                |   |  |  |

## 1. SIM - 220nF Capacitor, All Model Types

| Simulated<br>Measured<br>Both |                 | Capacitor Models |                 |                |  |  |  |  |

|-------------------------------|-----------------|------------------|-----------------|----------------|--|--|--|--|

| Value                         | Complex<br>VOID | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |  |  |  |  |

| 220nF                         | X               | Х                | Х               | X              |  |  |  |  |

| 150nF                         | Χ               | Χ                |                 | 7              |  |  |  |  |

| 47nF                          | X               | Χ                |                 |                |  |  |  |  |

| 22nF                          | X               | X                |                 |                |  |  |  |  |

## Model Comparison 56G Single Bit Response

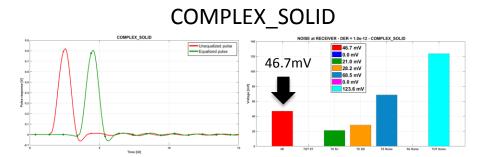

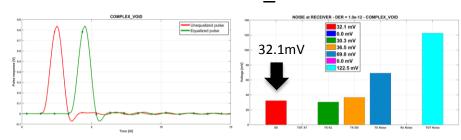

#### COMPLEX VOID

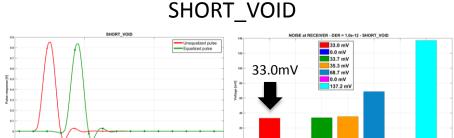

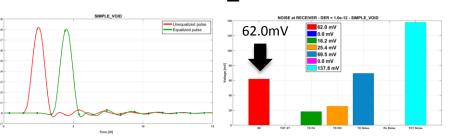

#### SIMPLE VOID

# 2 & 3. SIM / MEAS - All Measured Values (VOID & SOLID Configuration)

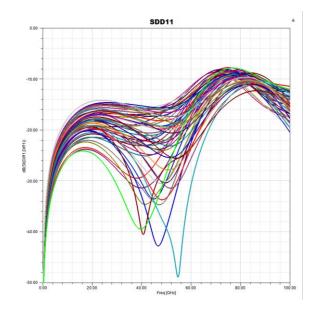

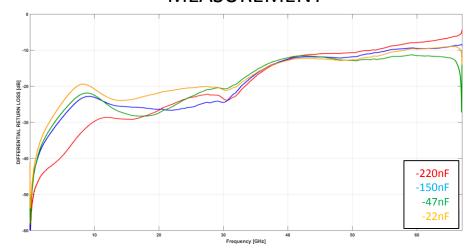

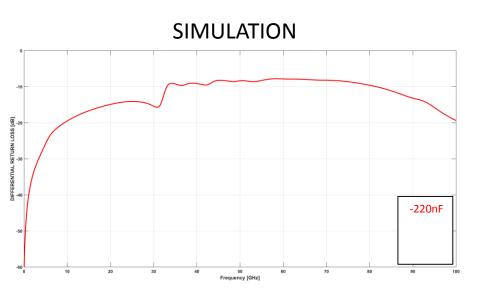

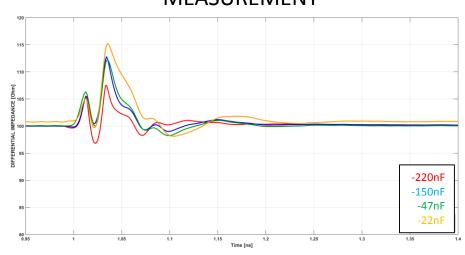

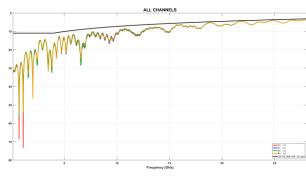

## 2. SIM vs MEAS - SDD11 (VOID)

| Simulated<br>Measured<br>Both |                 |                  |                 |                |

|-------------------------------|-----------------|------------------|-----------------|----------------|

| Value                         | Complex<br>VOID | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |

| 220nF                         | X               | Х                | Х               | Х              |

| 150nF                         | Χ               | X                |                 |                |

| 47nF                          | X               | X                |                 |                |

| 22nF                          | X               | X                |                 |                |

2

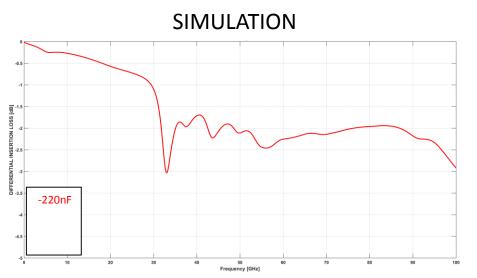

# SIMULATION Signature of the control of the control

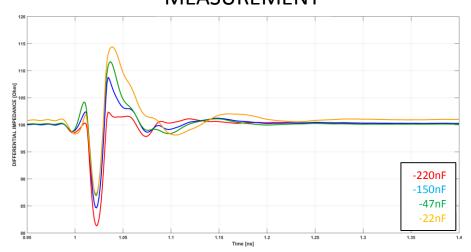

## 3. SIM vs MEAS - SDD11 (SOLID)

| Simulated<br>Measured<br>Both | Capacitor Models |                  |                 |                |  |  |

|-------------------------------|------------------|------------------|-----------------|----------------|--|--|

| Value                         | Complex<br>VOID  | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |  |  |

| 220nF                         | X                | Х                | Х               | х )            |  |  |

| 150nF                         | Χ                | X                |                 |                |  |  |

| 47nF                          | Χ                | Χ                |                 |                |  |  |

| 22nF                          | Х                | X                |                 |                |  |  |

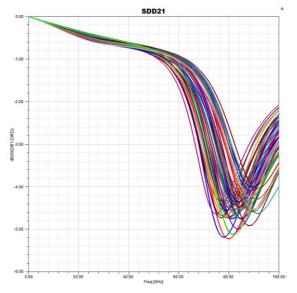

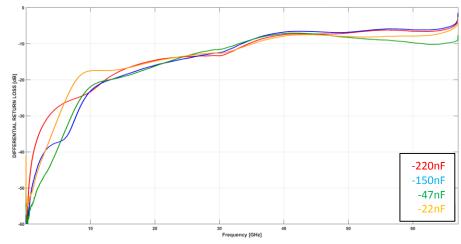

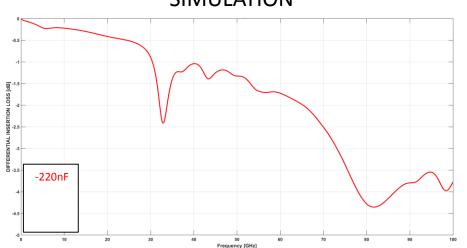

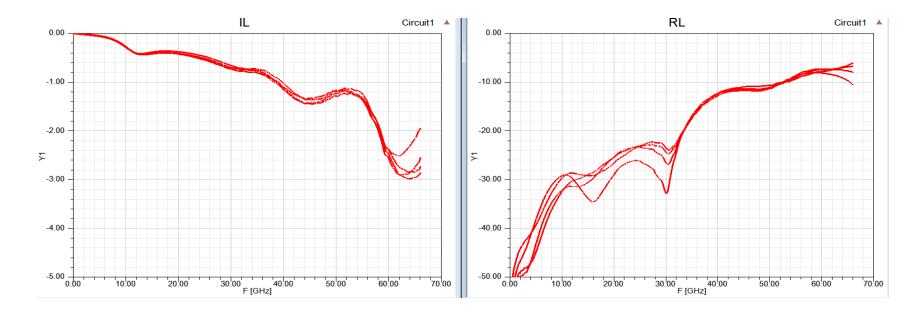

## 2. SIM vs MEAS - SDD21 (VOID)

| Simulated<br>Measured<br>Both |                 |                  |                 |                |

|-------------------------------|-----------------|------------------|-----------------|----------------|

| Value                         | Complex<br>VOID | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |

| 220nF                         | X               | X                | Х               | Х              |

| 150nF                         | Χ               | X                |                 |                |

| 47nF                          | Χ               | X                |                 |                |

| 22nF                          | X               | X                |                 |                |

2

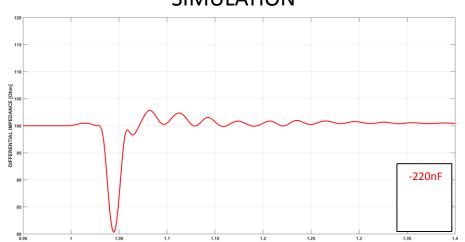

#### **SIMULATION**

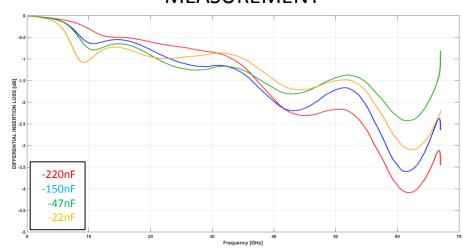

## 3. SIM vs MEAS - SDD21 (SOLID)

| Simulated<br>Measured<br>Both | Capacitor Models |                  |                 |                |  |  |

|-------------------------------|------------------|------------------|-----------------|----------------|--|--|

| Value                         | Complex<br>VOID  | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |  |  |

| 220nF                         | X                | Х                | Х               | х )            |  |  |

| 150nF                         | Χ                | X                |                 |                |  |  |

| 47nF                          | Χ                | Χ                |                 |                |  |  |

| 22nF                          | Х                | X                |                 |                |  |  |

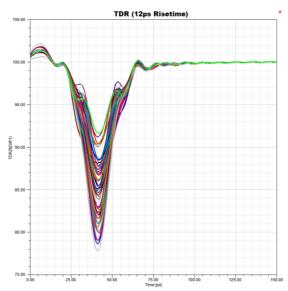

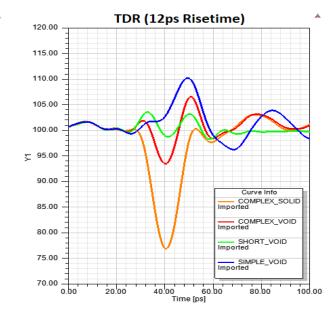

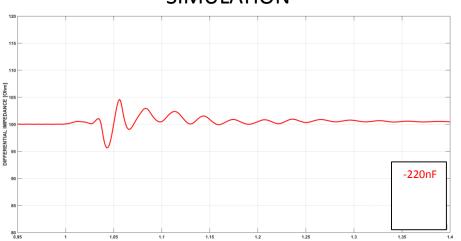

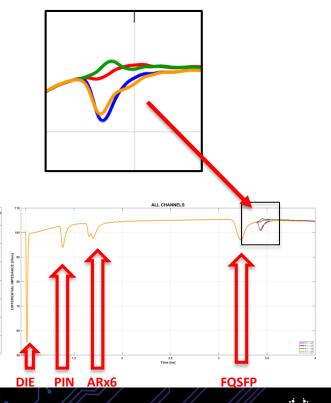

## 2. SIM vs MEAS – TDR, 12ps RT (VOID)

| Simulated<br>Measured<br>Both | Capacitor Models |                  |                 |                |  |

|-------------------------------|------------------|------------------|-----------------|----------------|--|

| Value                         | Complex<br>VOID  | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |  |

| 220nF                         | X                | Х                | Х               | Х              |  |

| 150nF                         | Х                | Χ                |                 |                |  |

| 47nF                          | Χ                | X                |                 |                |  |

| 22nF                          | X                | X                |                 |                |  |

2

#### **SIMULATION**

## 3. SIM vs MEAS - TDR, 12ps RT (SOLID)

| Simulated<br>Measured<br>Both | Capacitor Models |                  |                 |                |  |  |

|-------------------------------|------------------|------------------|-----------------|----------------|--|--|

| Value                         | Complex<br>VOID  | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |  |  |

| 220nF                         | X                | X                | Х               | X              |  |  |

| 150nF                         | Χ                | Χ                |                 |                |  |  |

| 47nF                          | Χ                | X                |                 |                |  |  |

| 22nF                          | X                | X                |                 |                |  |  |

#### **SIMULATION**

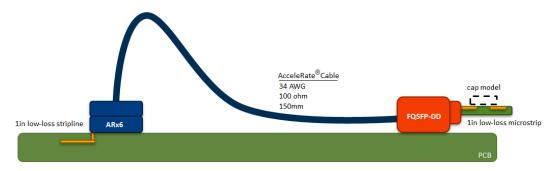

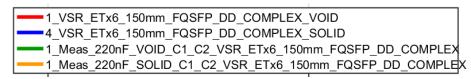

## 4. Chip to Module Exploration

## **Simulation to Measurement Comparison**

## 220nF DC Blocking cap with Host Board package only:

- 56G NRZ

- 112G PAM4

- 112G PAM4, 1 TAP DFE

- 112G PAM4, 3 TAP DFE

- 112G PAM4, 12 TAP DFE

|   | Simulated<br>Measured<br>Both | Capacitor Models |                  |                 |                |  |  |

|---|-------------------------------|------------------|------------------|-----------------|----------------|--|--|

|   | Value                         | Complex<br>VOID  | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |  |  |

| 4 | 220nF                         | X                | Х                | Х               | Х              |  |  |

|   | 150nF                         | Χ                | Χ                |                 |                |  |  |

|   | 47nF                          | Χ                | Χ                |                 |                |  |  |

|   | 22nF                          | X                | X                |                 |                |  |  |

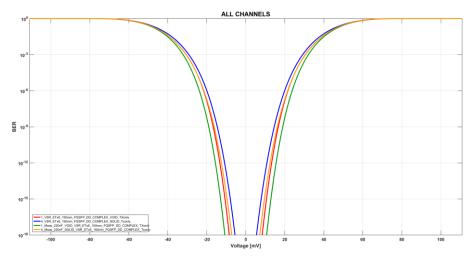

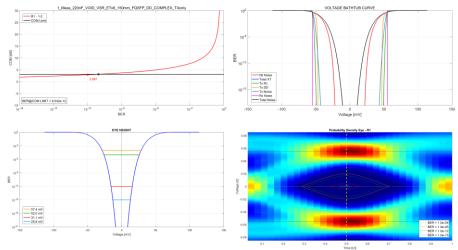

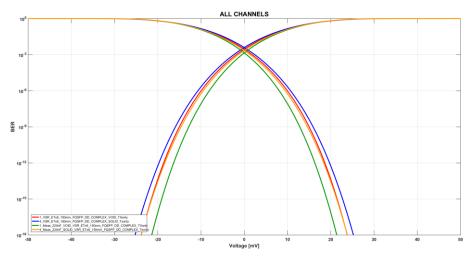

## 4. Host Package Only Study

## **Includes TX Package & 220nF Cap**

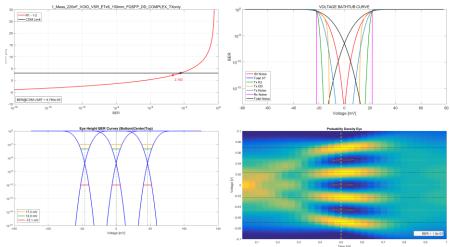

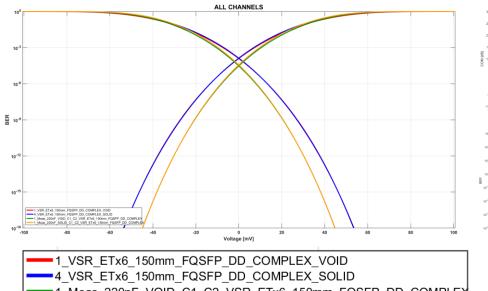

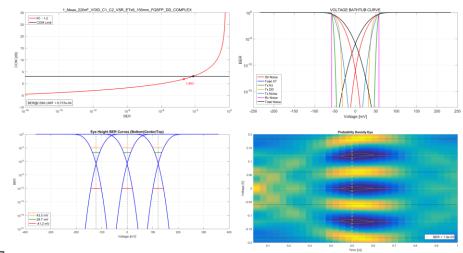

## **56G NRZ**

#### Voltage Bathtub - All Cases

1\_VSR\_ETx6\_150mm\_FQSFP\_DD\_COMPLEX\_VOID

4\_VSR\_ETx6\_150mm\_FQSFP\_DD\_COMPLEX\_SOLID

1\_Meas\_220nF\_VOID\_C1\_C2\_VSR\_ETx6\_150mm\_FQSFP\_DD\_COMPLEX

1\_Meas\_220nF\_SOLID\_C1\_C2\_VSR\_ETx6\_150mm\_FQSFP\_DD\_COMPLEX

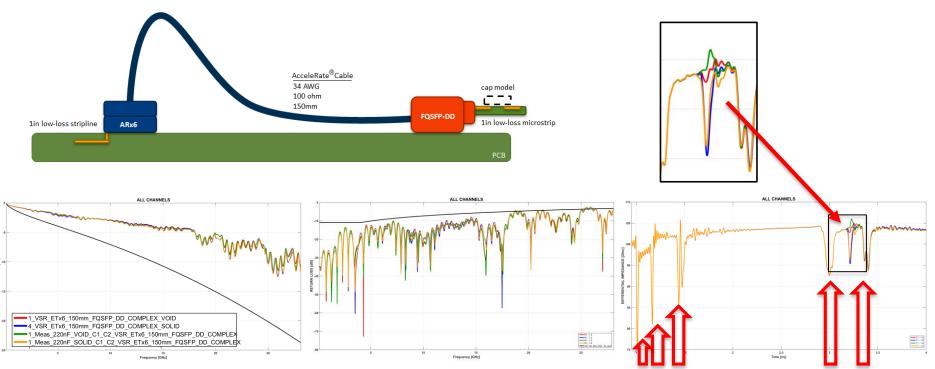

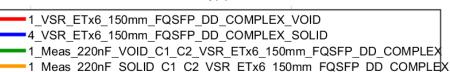

## **112G PAM4**

#### Voltage Bathtub - All Cases

#### Measured VOID

1\_VSR\_ETx6\_150mm\_FQSFP\_DD\_COMPLEX\_VOID

4\_VSR\_ETx6\_150mm\_FQSFP\_DD\_COMPLEX\_SOLID

1\_Meas\_220nF\_VOID\_C1\_C2\_VSR\_ETx6\_150mm\_FQSFP\_DD\_COMPLEX

1\_Meas\_220nF\_SOLID\_C1\_C2\_VSR\_ETx6\_150mm\_FQSFP\_DD\_COMPLEX

#### 112G PAM4 3 TAP DFE

#### Voltage Bathtub - All Cases

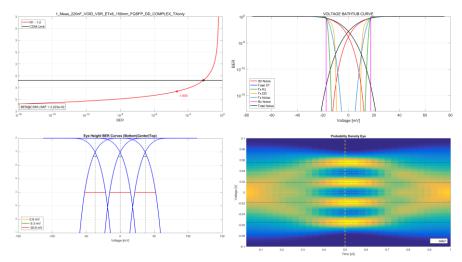

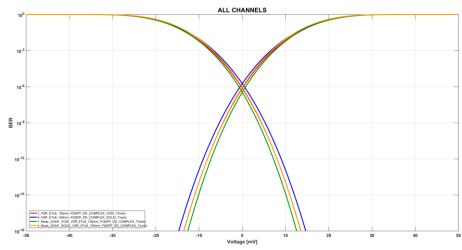

## 5. Chip to Module Exploration

## **Simulation to Measurement Comparison**

## 220nF DC Blocking cap with optimistic TX/RX package:

- 56G NRZ

- 112G PAM4

- 112G PAM4, 1 TAP DFE

- 112G PAM4, 3 TAP DFE

- 112G PAM4, 12 TAP DFE

|   | Simulated<br>Measured<br>Both | Capacitor Models |                  |                 |                |

|---|-------------------------------|------------------|------------------|-----------------|----------------|

| 5 | Value                         | Complex<br>VOID  | Complex<br>SOLID | Shorted<br>VOID | Simple<br>VOID |

|   | 220nF                         | X                | Х                | Χ               | Х              |

|   | 150nF                         | Χ                | Χ                |                 |                |

|   | 47nF                          | Χ                | Χ                |                 |                |

|   | 22nF                          | X                | X                |                 |                |

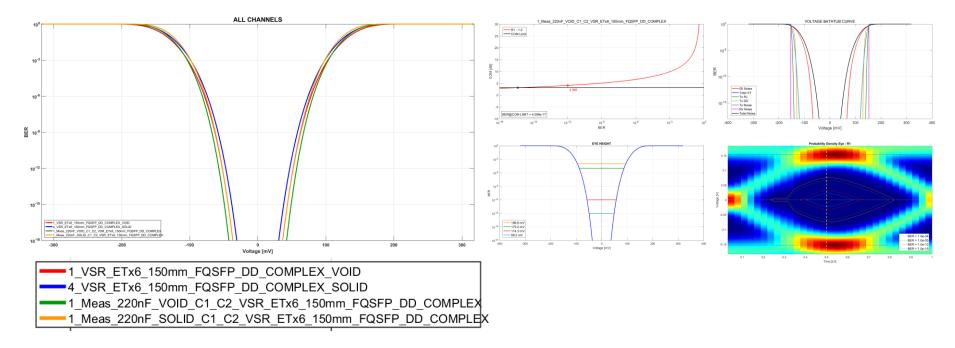

## 5. Optimistic Host/Module Package Study

## Includes TX/RX Package & 220nF Cap

**FQSFP PKG**

**DIE PIN ARx6**

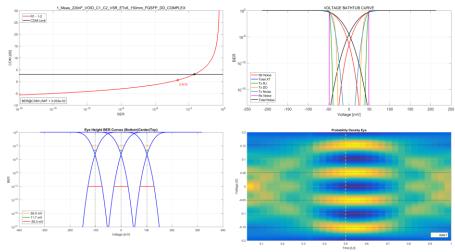

## **56G NRZ**

#### Voltage Bathtub - All Cases

#### Measured VOID

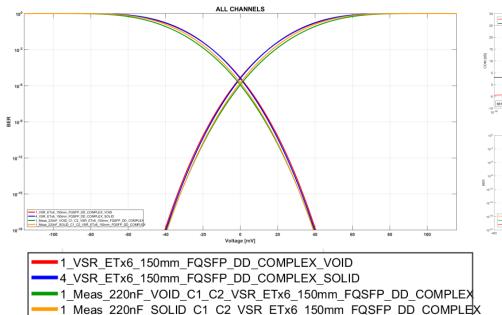

## **112G PAM4**

#### Voltage Bathtub - All Cases

#### Measured VOID

#### 112G PAM4 3 TAP DFE

#### Voltage Bathtub - All Cases

#### Measured VOID

# Test Vehicle Correlation Work VOID, SOLID, & CAL Layouts

#### **Test Vehicle Correlation Work**

#### **220nF VOID Measurements**

#### **Test Vehicle Correlation Work**

#### 220nF VOID Simulation v2.0

# Thank you!

**QUESTIONS?**